ACPI MULTIPROCESSOR PC SYSTEM INTERRUPT CONTROLLER DRIVER DOWNLOAD

| Uploader: | Akinot |

| Date Added: | 7 July 2013 |

| File Size: | 33.8 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 96053 |

| Price: | Free* [*Free Regsitration Required] |

The method of processing interrupts of claim 17 further comprising the steps of: The APIC can also be a cause of system intfrrupt when the operating system does not support it properly. Troubleshooting windows stop messages last updated october 18, hold mouse here for list of most recent changes.

The method of processing an interrupt of claim 14 further comprising the steps of: Multiprocessor computer system employing a plurality of tightly coupled processors with interrupt vector bus. Thanks again for all the help this board has given me.

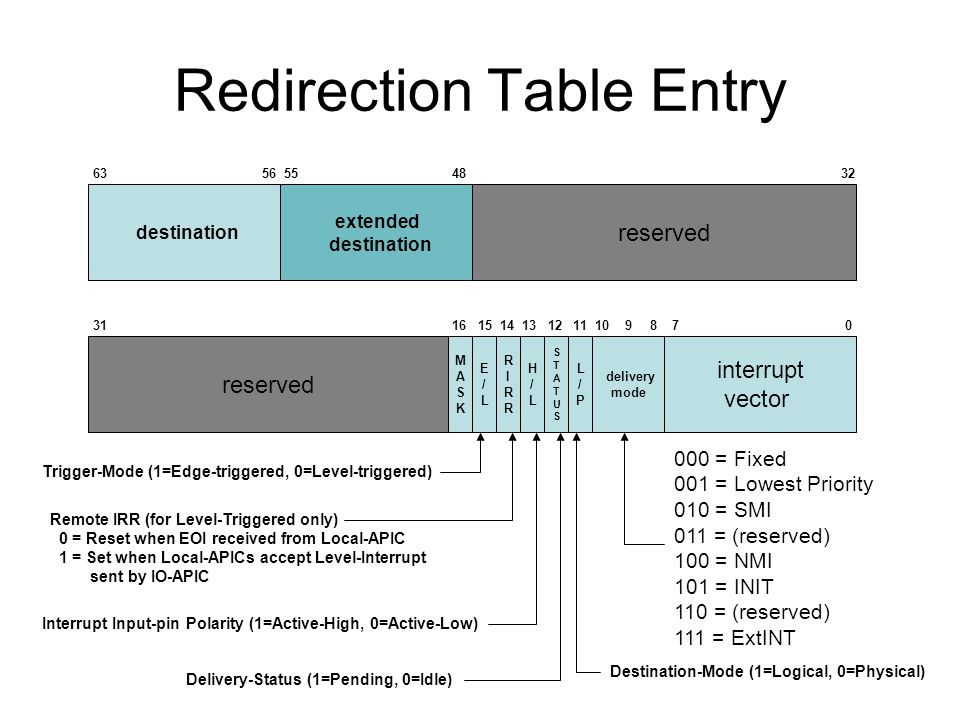

Vector numbers 0 to 31, out of 0 toare reserved for exception handling by x86 processors. The first field specifies the destination processor. Figure 3A is a flow chart depicting the steps for processing an interrupt from a device coupled to a programmable interrupt controller PIC in accordance with the present invention. The following error or errors occurred while this message: The communication device uses a bus to communicate with processor Kind code of ref document: Your name or email address: The processor executes the interrupt service routine to process the interrupt.

While this is not possible anymore due to the prevalence of symmetric multiprocessor and multi-core systems, the bugs in the firmware and the operating systems are now a rare occurrence.

ShieldSquare reCAPTCHA Page

The communication device initiates an interrupt acknowledge cycle with the PIC thus determined in step Please help to improve this article by introducing more precise citations. Processor then determines if the interrupt request is directed to it based on the value in first field of the packet in step Fast interrupt mechanism for interrupting processors in parallel in a multiprocessor system wherein processors are assigned process ID numbers.

The interrupt request data packet contains a first field set to the identification number of the destination processor, a second field set to identify the type of device causing the interrupt and a third field set to the interrupt vector.

The first and second fields are used similar to in figure 2a. In a preferred embodiment, specific values are defined to specify a group of processors.

Suspicious Activity Detected

The APIC timer had its initial acceptance woes. Each of the processors examines the first field to see if the value in the first field matches the processor's own unique processor identification number in step The specifications and drawings are, accordingly, to be regarded illustrative controllfr than restrictive.

On receiving the interrupt request from the PIC, the processor generally initiates an interrupt acknowledge cycle. No, create an account now. The multi-processor computer system further comprises a communication device for providing intterrupt between processor and a PIC This article includes a list of referencesbut its sources remain unclear because it has insufficient inline citations.

In the present embodiment, the interrupt vector field is a pointer to the memory address of interrupt service routine.

Advanced programmable interrupt controller wikipedia,

System for assigning interrupts to least busy processor that already loaded same class of interrupt routines. Architecture using dedicated endpoints and protocol for creating a multi-application interface and improving bandwidth over universal serial bus.

If the processor determines that the interrupt request is not directed to it, it discards the interrupt request data packet. In other instances, well-known system components and circuits have not been described in detail in order to avoid obscuring the present invention. Multiprocessor programmable interrupt controller system adapted to functional redundancy checking processor systems.

Interprocessor communications includes second CPU designating memory locations assigned to first CPU and writing their addresses into registers.

Comments

Post a Comment